超越 PCB:高速問題的系統級考慮

當系統從數百兆發展到數十千兆時,芯片設計、封裝設計和系統設計不再能夠分開考慮。 對于高端產品,設計芯片時要考慮封裝設計和系統設計。

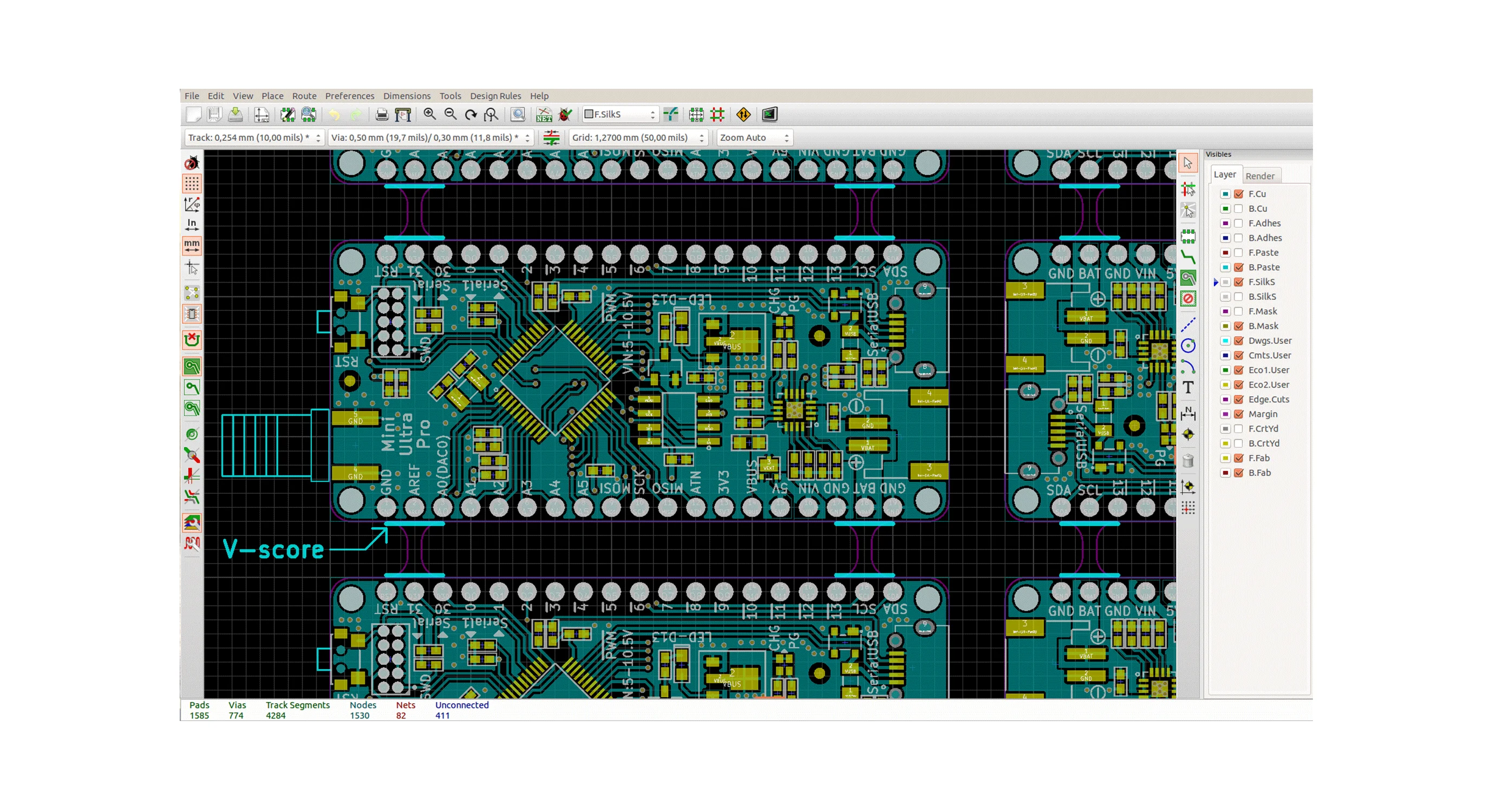

在排除軟件本身的問題之后,如何簡化流程,減少工程師在過程中的失誤,讓工程師能夠將更多的精力投入到設計中,讓產品盡快進入市場也成為了我們需要解決的內容。 EDA廠商正在考慮。

通常,系統上的連接線從硅的 I/O 開始,穿過封裝的凸塊和子集,到達封裝引腳,然后穿過 PCB 到達其他封裝引腳、子集、凸塊和 I /O 芯片。 芯片、封裝和電路板是三個不同的領域。 以前的工程師在設計時沒有考慮周全,也不知道其他工程師的想法。 但隨著設計頻率的提高、芯片面積的縮小、設計周期的縮短,廠商在設計芯片時應兼顧封裝設計和PCB設計,將三者有效結合起來。 陳蘭冰表示,“這個時候,無論是從信號完整性還是設計周期的角度,我們都應該同時考慮SilICon Package board的設計,協調好它們之間的相互關系。比如有時會出現時序問題,很難解決。” 在 PCB 中解決,但在封裝中可以輕松解決。”

CADence作為系統級工藝設計的積極倡導者,其Allegro平臺涵蓋板級設計和封裝級設計,可以與Cadence的其他多個芯片設計平臺連接,形成完整的設計鏈,實現有效的數據交換和通信。 此外,Cadence的VSIC(Virtual System InterConnect)設計方法是一種全新的Silicon Package Board協同設計方法,可以讓工程師在設計初期就考慮到整個系統帶來的時序或信號完整性問題,解決了設計中的一大瓶頸。 千兆赫信號的設計。

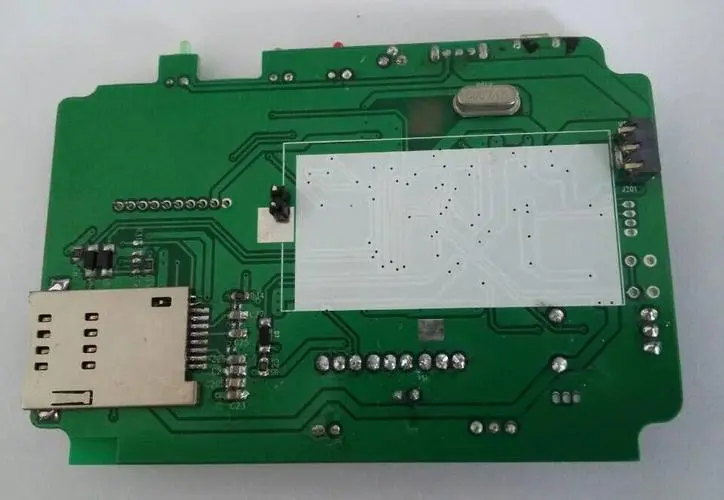

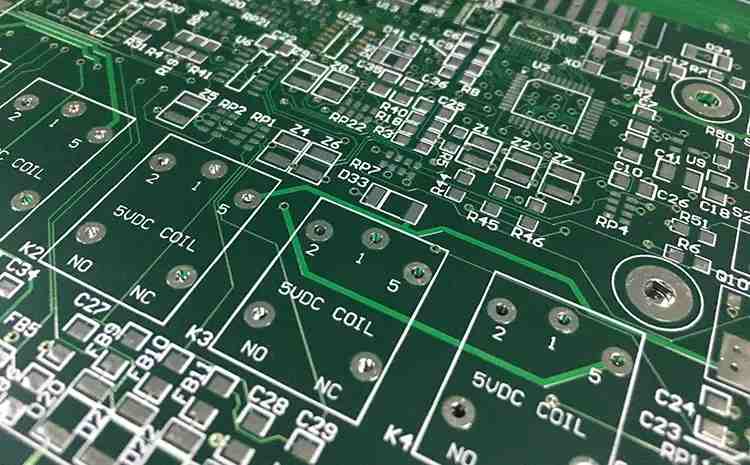

---- 電路板組裝及電路板加工廠商講解高速高密度PCB設計面臨的新挑戰:系統級的高速考慮。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱