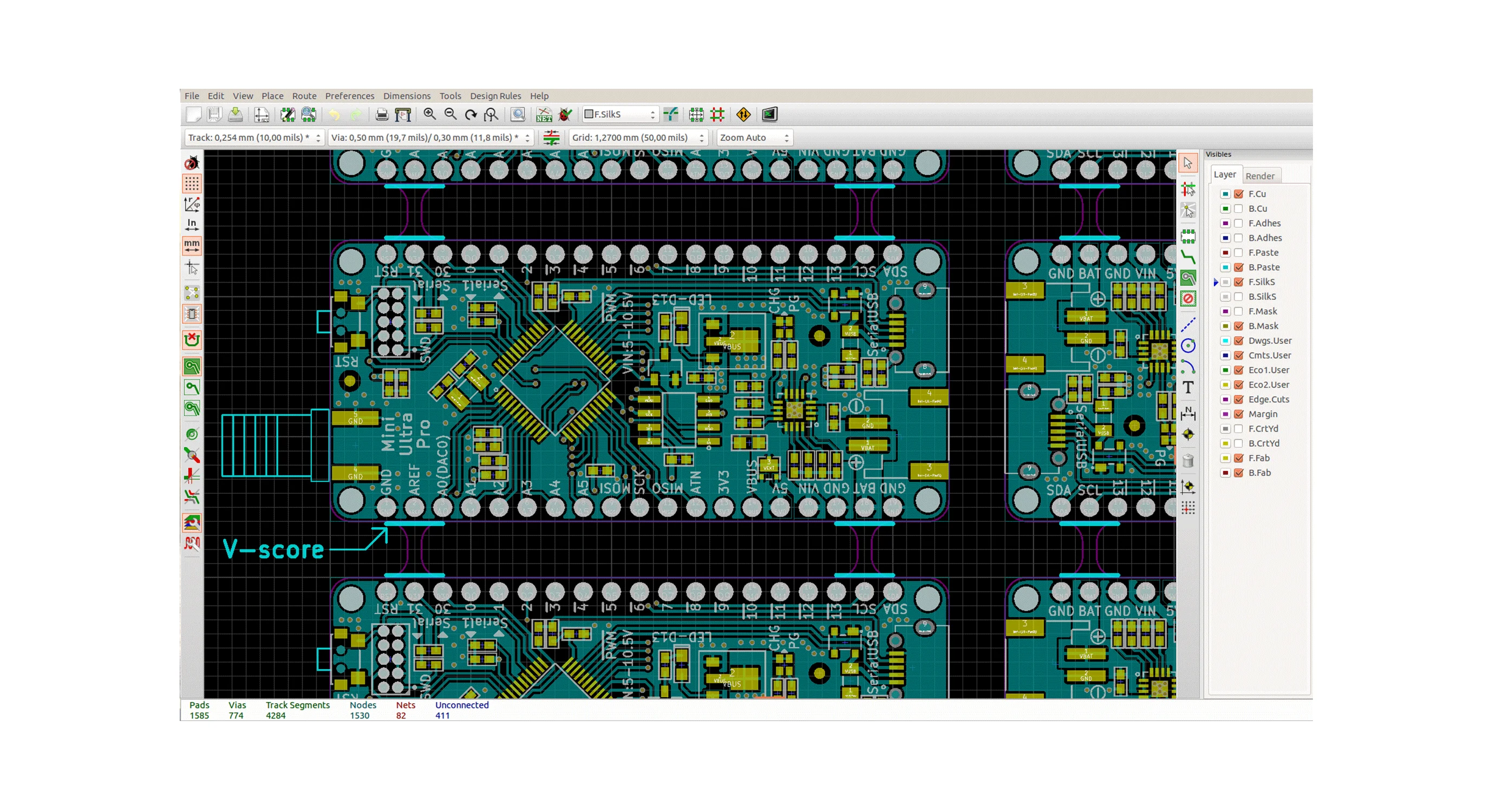

電路板設計的基本過程可以分為三個步驟:電路原理圖的設計、網絡表的生成、印刷電路板的設計。無論是板上的器件布局還是布線,都有特定的要求。

例如,輸入和輸出接線不應平行,以避免干擾。如果兩條信號線并行走線,則應通過地線隔離。相鄰兩層應盡可能相互垂直。寄生耦合很可能并聯發生。 電源線和地線應盡可能分為兩層,相互垂直。線寬方面,可以用較寬的地線作為數字電路PCB的回路,形成地網格(模擬電路不能這樣用),可以鋪大面積的銅。下面百能小編為大家講解一下單片機控制板PCB設計的原理以及需要注意的一些細節。

組件布局在組件布局方面,相關組件應盡可能靠近放置。例如,時鐘發生器、晶振和CPU的時鐘輸入端容易產生噪聲,因此應放置得較近。對于那些容易產生噪聲的器件、小電流電路、大電流電路開關電路等,應盡可能遠離單片機的邏輯控制電路和存儲電路(ROM、RAM)。如果可能的話,可以將這些電路單獨制作成電路板,這樣有利于抗干擾,提高電路的可靠性。

去耦電容應安裝在關鍵器件附近,如ROM、RAM等芯片。 事實上,印刷電路板的布線、引腳布線和布線都可能產生較大的電感效應。大電感可能會導致 Vcc 接線上產生嚴重的開關噪聲尖峰。防止 Vcc 布線上出現開關噪聲尖峰的唯一方法是在 VCC 和電源接地之間放置一個 0.1uF 電子去耦電容器。 如果電路板上使用表面貼裝元件,可以使用貼片電容直接靠在元件上,固定在Vcc引腳上。 最好使用陶瓷片式電容器,因為它具有低靜電損耗 (ESL) 和高頻阻抗。 另外,這種電容器在溫度和時間上的介電穩定性也非常好。 鉭電容盡量不要使用,因為高頻時阻抗較高。

放置去耦電容時應注意以下幾點:

在印刷電路板的電源輸入端連接一個約100uF的電解電容。 如果體積允許的話,電容最好大一些。

原則上每個集成電路芯片旁邊應放置一個0.01uF的陶瓷貼片電容。如果電路板間隙太小無法放置,可每10個芯片左右放置1-10個鉭電容。

對于抗干擾能力較弱、關斷時電流變化較大的器件、RAM、ROM等存儲器件,電源線(Vcc)與地線之間應接去耦電容嗎? 電容器的引線不能太長,特別是高頻旁路電容器不能有引線。

地線設計在單片機控制系統中,地線的種類有很多種,如系統地、屏蔽地、邏輯地、模擬地等。地線布置是否合理,將決定抗干擾能力。 電路板的抗干擾能力。 設計接地線和接地點時,應考慮以下問題:

邏輯地和模擬地應分開接線,不能混用。 將各自的地線分別連接到相應的電源地線上。設計時,模擬地線應盡可能加粗,并盡可能增大引出端接地面積。 一般來說,通過光耦將輸入輸出模擬信號與單片機電路隔離比較好。

在設計邏輯電路印制電路板時,其地線應形成閉環形式,以提高電路的抗干擾能力。

接地線應盡可能粗。如果地線很細,地線的電阻就會很大,導致地電位隨著電流的變化而變化,導致信號電平不穩定,降低電路的抗干擾能力。如果布線空間允許,主地線的寬度至少應為2-3mm,元件引腳上的地線應為1.5mm左右。

注意接地點的選擇。當電路板上的信號頻率低于1MHz時,由于布線和元件之間的電磁感應影響不大,而接地電路形成的環流對干擾影響較大,因此應采用一點接地。防止其形成循環。當電路板上的信號頻率高于10MHz時,由于PCB布線設計的明顯電感效應,地線阻抗變大,接地電路形成的環流不再是主要問題。因此,應采用多點接地,盡量減小地線阻抗。

對于其他電源線的布局,PCB布線設計時除了根據電流大小盡可能加寬布線寬度外,電源線、地線的布線方向應與數據線的布線方向保持一致。PCB布線設計結束時,應在電路板底層沒有布線的地方鋪上地線。這些方法都有助于增強電路的抗干擾能力。

數據線的寬度應盡可能寬,以降低阻抗。數據線的寬度至少不應小于0.3mm(12mil)。如果使用0.46~0.5mm(18mil~20mil)則更為理想。

由于電路板的一個過孔會帶來10pF左右的電容效應,會對高頻電路引入過多的干擾,因此在PCB布線設計時應盡可能減少過孔的數量。而且,過多的過孔也會降低電路板的機械強度。

然后

聯系

電話熱線

13410863085Q Q

微信

- 郵箱