PCB Design of RF Switch Module Function Circuit

With the development of modern wireless communICation systems, mobile communication, radar, satellite communication and other communication systems have higher requirements for switching speed, power capacity and integration of transceiver switches Therefore, the research and development of busbar technology is to meet the special requirements of military, and the busbar module is of great significance We will use the idea of virtual instrument to implement hardware circuit in software The RF switch designed below can be directly controlLED by a computer and can be easily integrated with the bus test system The application of computer and microelectronics technology in today's testing field has broad prOSPects

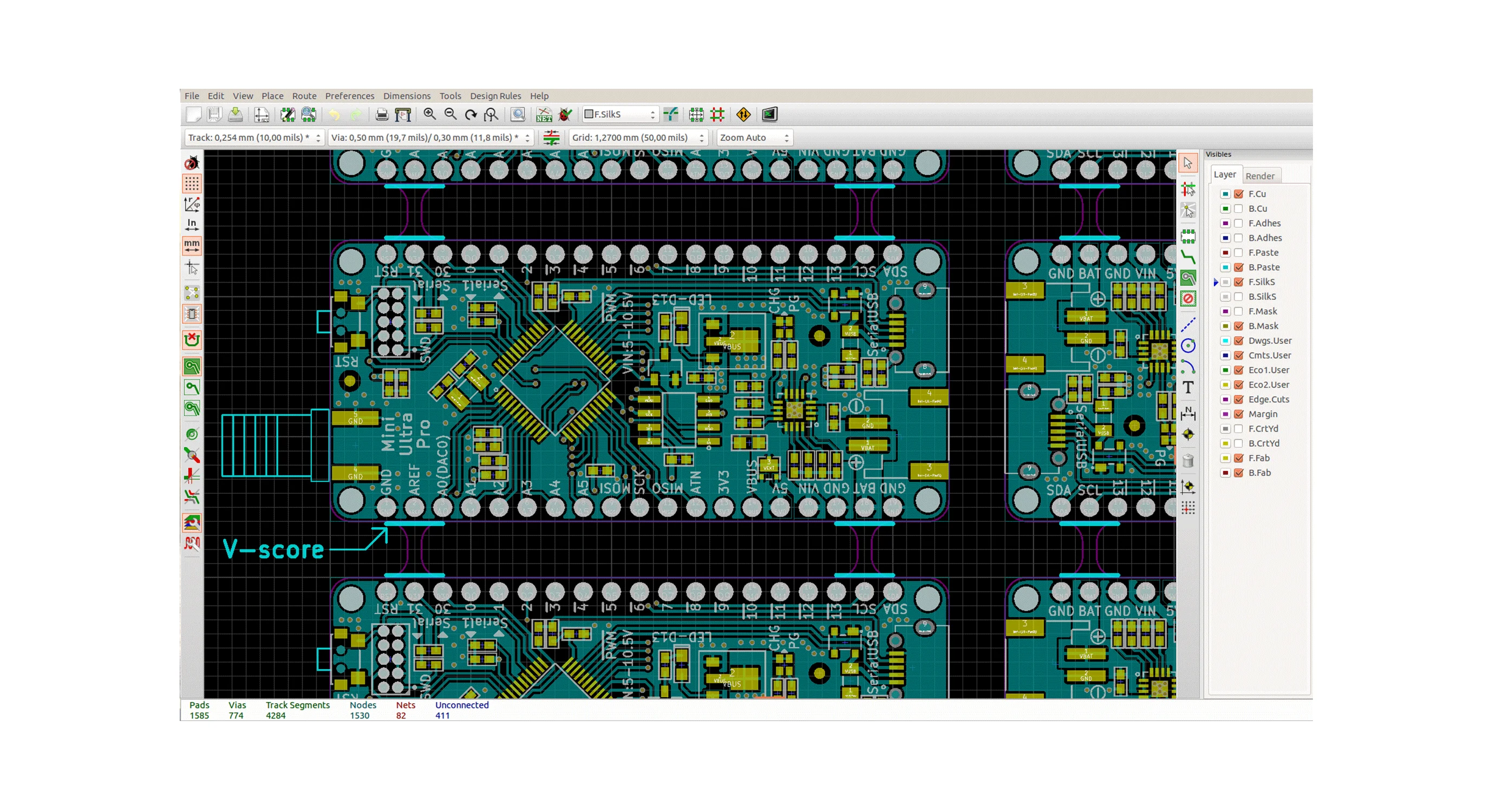

PCB board

1. Design and implementation of VXI bus interface circuit

VXIbus is an extension of VMEbus in this field of instrumentation It relies on effective standardization and adopts modular method to realize serialization, generalization, interchangeability and interoperability of VXI bus bar instruments Its open architecture and plug and play model fully meet the needs of information products It has the advantages of high-speed data transmission, compact structure, flexible configuration and good electromagnetic compatibility Therefore, the system is very convenient to set up and use, and its application is more and more extensive It has gradually become the bus of high performance test system integration

VXI bus bar is a fully open modular instrument backplane bus bar specification, applicable to various instrument manufacturers VXI bus devices are mainly divided into register based devices, MESsage based devices, and memory based devices The current promotion of register based devices in applications (about 70%) VXI bus register base interface circuit mainly includes four parts: bus buffer drive, addressing and decoding circuit, data transmission response state machine, and configuration and operation register group In the four parts, except the bus buffer driver is implemented by 74ALS245 chip, the rest is implemented by FPGA Use a FLEX10K chip EPF10K10QC208-3 and an EPROM core EPC1441P8, and the corresponding software MAX+PLUS2 is used for design and implementation

1.1 Bus buffer driver

This part completes the buffer receiving or driving of the data line For A16/D16 devices, only buffer drive of backplane data bus D00D15 is realized According to the requirements of the VXI bus specification, this part is implemented by two 74LS245s, which are strict by DBEN * (produced by the data transmission response state machine)

1.2 Addressing and decoding circuit

Addressing lines include address lines A01 to A31, data strobe DS1 * 0 * * and DS1 *, and long text line LWORD * * The control lines include the address strobe line AS * and the read/write signal line write * * The design of this circuit adopts the schematIC design method of MAX+PLUS2. Use the existing components in the component library to design, using two 74688 and one 74138. When the function module decodes the address line A15A01 and the address modification line AM5AM0. When the device is addressing, it receives the address information on the address line and the address modification line, and connects it with the logical address LA7 è set by the hardware address switch on the module ?? LA0 for comparison If the logical value on AM5AM0 is 29H or 2DH (Because it is an A16/D16 device), when the address lines A15 and A14 are both 1, A13 è ?? The logical value on A06 is equal to the logical address of the module, the device is addressed and strobed (CADDR * is true) Then send the result to the lower decoding control, and select the register of the module in the 16 bit address space through the decoding address A01A05

1.3 Data transmission response state machine

The data transmission bus is a group of high speed asynchronous parallel data transmission buses, which is the main component of VMEbus system information exchange The signal lines of the data transmission bus can be divided into three groups: address lines, data lines, and control lines The design of this part adopts MAX+PLUS2 text input design method. Due to the time complexity of DTACK * *, it is designed and implemented by state machine using AHDL language This functional module includes control signals in the VXI backplane bus, and provides timing and control signals for the standard data transmission cycle (generating the data transmission enable signal DBEN *, the response signal DTACK * required by the bus to complete the data transmission, etc.) During data transmission, the system controller first addresses the module and sets the corresponding address strobe lines as * *, data strobe lines DS0 *, DS1 *, and WRITE * signal lines that control the direction of data transmission to be valid Level When the module detects that the address matches and the control line is valid, drive DTACK * to low level to confirm to the bus controller that the data has been placed on the data bus (read cycle) or data has been successfully received (write cycle))

1.4 Configuration Register

Each VXI bus device has a set of "configuration registers". The main controller of the system obtains some basic configuration information of VXI bus devices by reading the contents of these registers, such as device type, model, manufacturer, address space (A16, A24), A32) and the required storage space, etc The basic configuration registers of VXI bus devices include: identification register, device type register, status register, and control register The design of this part of the circuit adapters the MAX+PLUS2 schematic design method uses 74541 chips and the function modules created by them ID, DT, ST registers are read-only registers, and control registers are read-only registers In this design, VXI bus bars are mainly used to control the on-off of these switches. As a result, as long as you write the data into the channel register, you can control the on-off or pull on status of the relay switch, query the relay status, and read the data from the channel register According to the design requirements of the module, appropriate contents are written in the corresponding data bits to effectively control the RF switch of the functional module

2. Design module function circuit board

Each VXI bus device has a set of "configuration registers". The main controller of the system obtains some basic configuration information of VXI bus devices by reading the contents of these registers, such as device type, model, manufacturer, address space (A16, A24), A32) and the required storage space, etc The frequency range of RF circuit is about 10kHz to 300GHz With the increase of frequency, RF circuit has some characteristics different from low frequency circuit and DC circuit Therefore, when designing RF circuit board, we should pay special attention to the influence of RF signal on circuit board RF switch circuit is controlled by VXI bus bar In order to reduce the interference in the design, the bus interface circuit part and the RF switch functional circuit are connected through flat cables The following mainly introduces the design of PCB RF switch functional circuit

2.1 Layout of components

Electromagnetic compatibility (EMC) refers to the ability of an electronic system to work normally in accordance with design requirements in a prescribed electromagnetic environment. For RF circuit PCB design, electromagnetic compatibility requires that each circuit module should not generate electromagnetic radiation as far as possible, and have certain anti electromagnetic interference capability The layout of components directly affects the interference and anti-interference capability of the circuit itself It also directly affects the efficiency of the designed circuit General principle of layout: components should be arranged along the same direction as far as possible. By selecting the direction of PCB entering the welding system, poor welding can be reduced or even avoided; There must be at least 0 The spacing between components is 5 mm to meet the welding requirements of components. If the PCB allows, the spacing between components should be as wide as possible Reasonable layout of components is also a prerequisite for reasonable wiring, so it should be considered comprehensively In this design, the relay is used to convert the RF signal channel. In addition, the relay should be as close to the signal input and output as possible to minimize the length of the RF signal line and reasonably wire for the next step Consider In addition, RF switch circuit is controlled by VXI bus, and the influence of RF signal on VXI bus control signal must be considered in layout

然后

聯(lián)系

電話熱線

13410863085Q Q

微信

- 郵箱